An AMD patent application document has come to light which could provide some interesting indications of one way new CPUs may be designed by the firm in the coming months / years. The US patent document concerns an "Instruction subset implementation for low power operation". Computing and prog rock music fan Underfox of Twitter unearthed this document at the weekend and shared a link to the patent PDF.

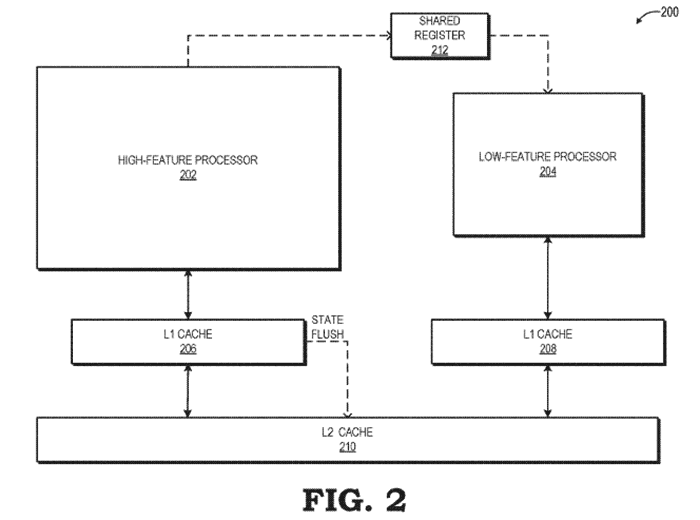

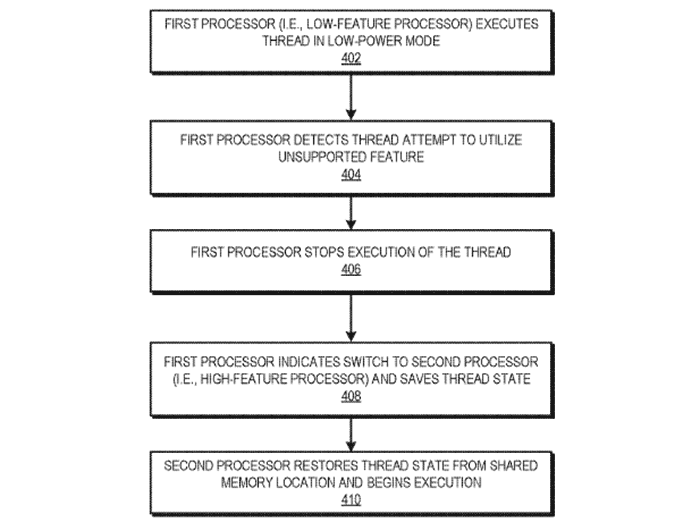

In brief it seems that AMD is trying to patent a heterogeneous processor which mixes full or "high-feature" CPU cores with "low-feature" CPU cores implementing a subset of ISA features. The obvious reference to Arm's 'big.LITTLE' implementation is made by Underfox, and you can cast an eye at Intel's Lakefield hybrid architecture too, if you are looking for inter-industry comparisons.

Another detail that makes AMD's patent look similar to ideas already in use by Arm and Intel is simply the purpose of the hybrid architecture - power saving. "The lower-feature second processor is configured to execute an instruction thread by consuming less power and with lower performance that the first processor," sums up the abstract.

AMD's background detail in the patent discusses the appeal of this hybrid architecture in mobile computing - with its wide performance range targets according to workload requirements. In mobile computing battery life is a major consideration.

In the proposed architecture, low-feature processor cores will be able to turn off high-feature processors when not in use. It is thus important that the low-feature cores have support for various low-priority processes that run frequently if not constantly - OS maintenance, timer support, monitoring functionality and so on.

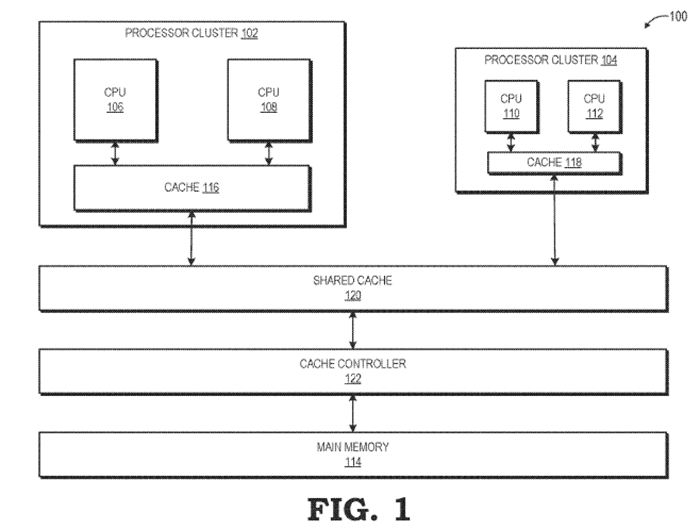

Various figures are provided in the patent document. One shows how the low-and high-feature processor clusters have a shared cache, controller and main memory access. For communication between the core clusters there are several options available and illustrated in patent diagrams.

Last but not least please remember that patent applications don't necessarily result in finished shipping products.