Researchers based at Purdue University have developed a new type of chip cooling system which uses an intricate series of tiny microchannels through which coolant courses. What is particularly impressive about the research thus far is that a cooling capacity of 1,000 watts per square centimetre has been demonstrated in lab tests.

As HEXUS readers will be well aware, conventional chip cooling uses attached heat-sinks and cooling water blocks or simple fans. This style of cooler isn’t up to scratch for an emerging class of high-performance electronics with 3D stacked processors. It would allow hotspots to form and hinder fast clock speeds. Justin A. Weibel, a research associate professor in Purdue’s School of Mechanical Engineering, points out that “As soon as you have even two chips stacked on top of each other the bottom one has to operate with significantly less power because it can’t be cooled directly.” Thus the idea of a cooling system embedded within the chip stack came about.

The researchers were funded by DARPA with a specific aim. The US defence body requested a cooling system that could tame chips “generating a kilowatt of heat per square centimetre, more than 10 times greater than in conventional high-performance computers”. Principal researcher of the project, Suresh V. Garimella, the Goodson Distinguished Professor of Mechanical Engineering at Purdue University, said the goal has been achieved, adding “This transformative approach has great promise for use in radar electronics, as well as in high-performance supercomputers. In this paper, we have demonstrated the technology and the unprecedented performance it provides”.

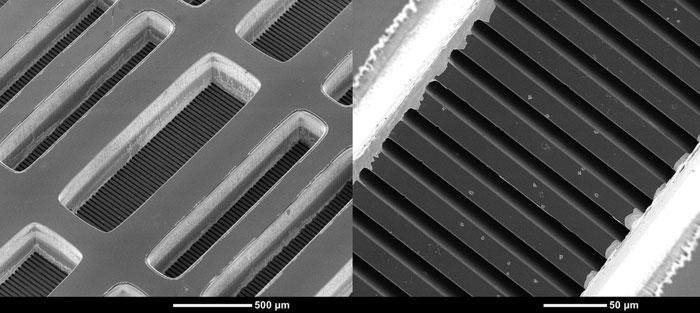

Interestingly the coolant used in the designs is a commercial product called HFE-7100, a dielectric, or electrically insulating fluid, meaning it won’t cause short circuits in the electronics. The Purdue University blog says that “as the fluid circulates over the heat source, it boils inside the microchannels,” the change of state providing optimal heat removal. Microchannels in the tested chips were reduced to just 15 or 10 microns in width, “which is about 10 times smaller than what is typical for microchannel cooling technologies,” Purdue doctoral student Kevin Drummond told the university news blog. Anoither detail important to the success of the cooling system was keeping the channels short: channel segments of just 250 microns in length were used.

A couple of years ago HEXUS reported on researchers at Georgia Tech, who demonstrated on-die liquid cooling via microfluidic passages etched into the silicon chips. This latest research doesn’t mention that particular prior work but has the similar stated aim of facilitating the stacking of multiple chips to allow much denser, higher-performance computing systems.