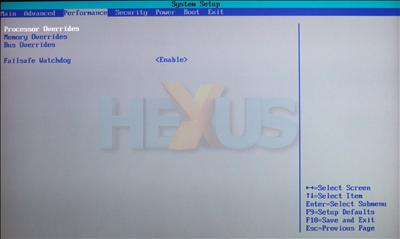

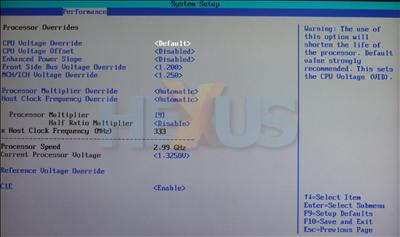

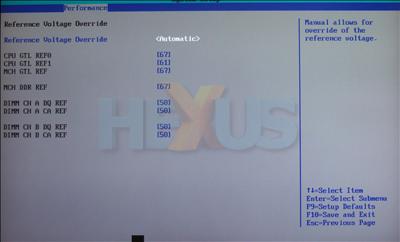

Intel DX48BT2 BIOS options

| |

|

|---|---|

| Item | Specifications |

| CPU FSB | 133-720MHz (1MHz increments) (533-2880MHz QDR Format) |

| CPU multiplier | CPU Min. (6x) – 40x (1x increments) |

| Memory clock | Reference frequency (200/266/333/400MHz) Memory frequency (800/1066/1333/1600MHz) |

| PCI-E clock | 100MHz-109.24MHz (1.32MHz increments) |

| PCI Clock | 33.33MHz - 35.64MHz*(0.33MHz increments) *tied to PCIe frequency |

| CPU voltage | 1.2875V - 1.6V (0.0125V increments) |

| CPU Voltage offset | +300mV |

| CPU PLL voltage | 1.50V-2.78V (0.02V increments) |

| Memory VDIMM | 1.50V-2.5V (0.04V increments) |

| Northbridge voltage | 1.25V-1.7V (0.025V increments) |

| FSB termination voltage | 1.10V-1.50V (0.025V increments) |

Discussion

The board provides a decent range of BIOS adjustments to cater to the overclocker, with higher FSB and voltage levels than are able to be run in practice. Cranking the voltage up to the maximum available settings could kill your expensive CPU or RAM within seconds, but the options remain for those looking towards more extreme methods to maintain stability at higher frequencies.The memory speeds are based on a ratio to FSB speeds. You set the ratio by choosing the reference frequency (FSB clock), and desired memory frequency. Using the available selections, ratios ranging from 2:1 to 1:2 - quad-pumped FSB:DDR3 RAM - are available. Whilst this method is inferior to independent FSB and memory clocking, if all the available options worked as expected there would be enough flexibility to get the most from your CPU and memory.

Gallery

CPU voltage defaults at 1.325V, rather than the normal 1.2V-1.2875V, although this is fine for a QX9650 running at stock speeds.

Our test board wouldn't work properly with most performance RAM modules that didn't feature XMP profiles stored in the SPD EEPROM.

Auto memory timings wouldn't work on modules with different SPD timings. The system was very unstable and won't even complete a couple of minutes in Memtest when set to Auto with modules with different timings installed, too.

A BIOS with plenty of options but, seemingly, poor at running with an eclectic array of memory.