But what about the chipset?

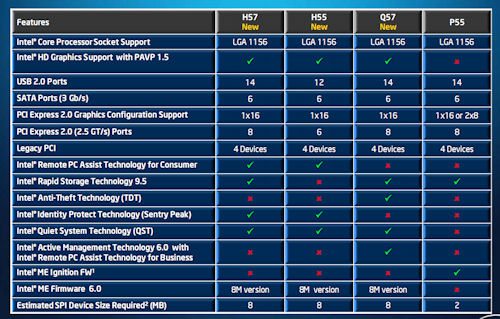

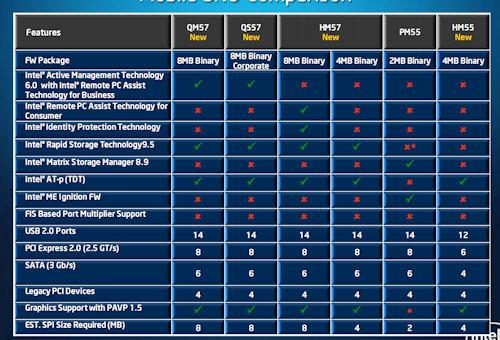

We've shown that the new 32nm chips have integrated graphics on the same package as the CPU and that they're presented on an LGA1156 form factor. The graphics portion dictates that new chipsets are released that support external display connectivity. As such, there will be three distinct chipsets from the get-go.The slides, below, stack them up against the also-desktop P55 range that support LGA1156 Lynnfield models. There will also be an updated P57 model that supports the FDI interface.

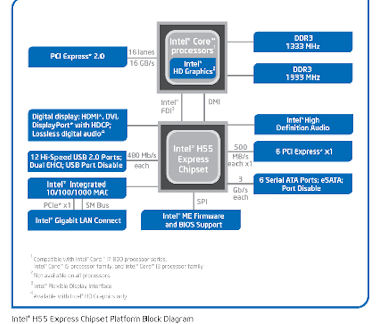

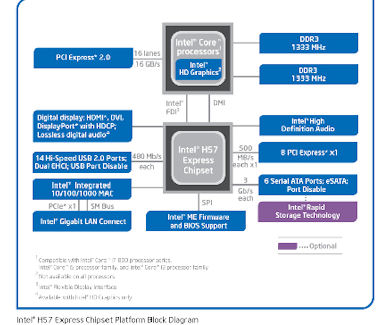

Primarily aimed at the home users, the H55 and H57 will be of interest to most readers. There isn't a whole lot to differentiate them, really. The H57 integrates a couple of extra USB 2.0 ports, has optional provision for Intel's Rapid Storage Technology (fancy name for esoteric RAID) and specifies a couple of extra PCIe 2.0 lanes for expansion.

The lack of differentiation is exemplified by comparing the two block diagrams, below.

What's important here is that both chipsets have the FDI connection between chip and chipset, making it possible to route the video out of the I/O section. The rest of the CPU-to-motherboard communication takes place over established DMI.

As per Lynnfield, the chip has 16 PCIe lanes that will hook up to a discrete graphics card, if needs be. There's no logical bifurcation for running dual-card CrossFireX or SLI, so motherboard manufacturers will either need to add PCIe lanes, or use some of the H5x's.

There's nothing revolutionary about either core-logic, USB 3.0 support is still at least a year off, Braidwood technology is conspicuous by its absence, but we can understand the lack of innovation because they're both aimed at the mainstream segment.

Boards for laptops will be even simpler, we imagine, and it'll be interesting to see how small the form factor can be made in light of the reduced number of ASICs required.