Bristol semiconductor firm XMOS has produced a sample piece of hardware that, with an arrangement of 16 of the company's CPUs, rivals the instruction throughput of a dual-core Intel CPU... for a third of the power consumption.

In the past two years or so the PC industry has seen growing momentum in the shift towards multi-core systems. With it comes a host of issues, the biggest of which might be how to get the most effective use out of a CPU that no longer has all of its power bottled up into a single element.

And if we look beyond the PC industry, towards embedded systems and communications applications, we see that these problems are already being solved.

XMOS is one such company creating the stimulus for change. Founded in July 2005, it is producing hardware based on its "XCore" CPU architecture that enables what is has termed "software defined silicon". The idea is to provide cheap, multi-core, multi-threaded processors for embedded systems development, that are quicker to develop for than FPGAs and less costly than custom ASIC designs.

And less than four years on it looks like it's getting there.

The company's current flagship processor is the XS1-G4. The chip contains four XCore tiles, each of which has access to 64KiB of SRAM on-chip, and can accommodate up to 8 software threads. Each XCore can push out 400MIPS and has communication channels between the other cores on the chip.

Communication between cores takes place over an "XLink", the protocol for which has been designed to scale up with many-core and many-chip designs, allowing routing of data across a network of XCores.

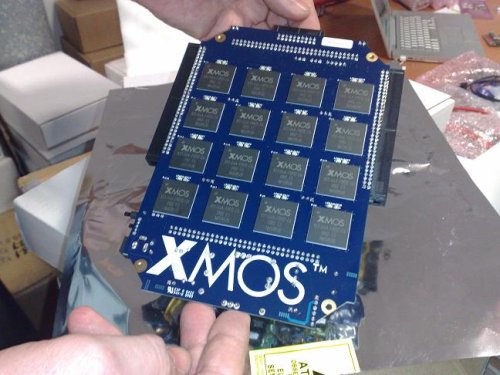

The company's experimental XMP-64 board demonstrates the scalability of the architecture, connecting 64 XCores in 16 G4 chips together on a single PCB that's smaller than a graphics card.

The end result is a board with the potential to crunch 25.6GIPS - or to put it another way, process almost as many instructions per second as Intel's Core 2 Extreme X6800. And it does it with less than 30 watts (as a quick refresher, the TDP of the X6800 is a princely 75W). It's not quite the 1800GFLOPS of a GeForce GTX 295, but it's a hell of a lot more flexible.

Speaking about the board on the company's developer community website, XMOS's Neil Richards envisages such setups as being ideal for image processing, target tracking, robotic control, and that the board "would make a great audio effects/synthesiser engine". Board porn inbound:

But all those chips are useless unless there's a decent way of programming 256 simultaneous threads. XMOS is onto that too.

It's adaptation of the C, predictably dubbed XC, brings the concept of communication channels into the language. It's this, combined with easy I/O and deterministic thread scheduling, that will allow programmers to implement full embedded systems and their interfaces completely in software, the company claims.

XMOS isn't the only company tackling multi-core in a big way right now. Bath firm picoChip specialises in many-core DSP chips for the communication industry.

Perhaps the efforts of these companies will see their concepts used beyond embedded and communication systems, giving us a decent way of programming for the many-core CPUs that are on the way on the next few years? In any case, expect these kinds of chips to be finding their way into your electronics gadgets.

Readers willing, we'll be taking a closer look at XMOS, so do let us know if you want to know more; leave us a comment!