Three dual-cores and a 16MB L3 cache - yes please!

As rival AMD gets its quad-core Barcelona chip out the door, it appears that Intel already has a six-core offering up its sleeve.

At a presentation in Austria last month, Intel discussed details of its upcoming server platforms with Sun and fortunately for the rest of us, slides supposedly from Intel's presentation found their way onto Sun's public web server over the weekend.

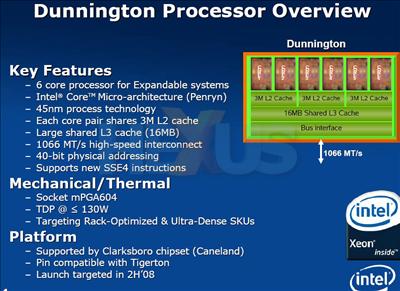

One slide, pictured below, outlines the successor to Intel's Tigerton Xeon; Dunnington. Based on its Penryn architecture, Dunnington could become Intel's first processor to feature three processor pairs, each sharing 3MBs L2 cache.

In addition to the L2 cache, all cores will also be able to utilise the huge 16MB L3 cache. Intel's slide states that Dunnington will be pin-compatible with Tigerton and support Intel's existing Clarksboro chipset. If the slides are to be believed, we'll be seeing Dunnington-based processors in the second half of 2008.

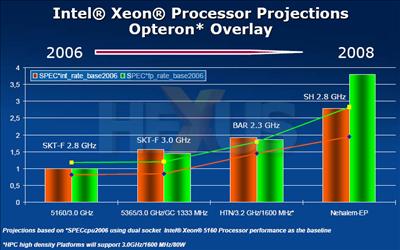

However, although Dunnington could prove to be yet another sharp thorn in AMD's side, it is merely the interim to Intel's next potentially fatal blow; Nehalem. Using the 45nm manufacturing methods of Intel's current Penryn, Nehalem is the planned successor to the Core micro architecture and is expected to debut late 2008 or early 2009.

A second leaked slide, pictured above, shows Intel's processor projections up to and including Nehalem. Although promising, it should be noted that these are indeed Intel's own projections and not actual benchmarks. Nonetheless, Nehalem's potential eight or more cores and integrated memory controllers hold plenty of potential. What, if anything, will AMD have to fight back?

Intel has so far declined to comment on the supposed leak of its presentation slides.